## CHASING THE "TAIL AT SCALE": TOWARD CLOUD-NATIVE ARCHITECTURES

## BY

## JOVAN STOJKOVIC

## DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate College of the University of Illinois Urbana-Champaign, 2025

## Urbana, Illinois

## Doctoral Committee:

Professor Josep Torrellas, Chair and Director of Research

Assistant Professor Tianyin Xu

Professor Darko Marinov

Associate Professor Jian Huang

Associate Professor Christina Delimitrou, Massachusetts Institute of Technology

Assistant Professor Dimitrios Skarlatos, Carnegie Mellon University

Dr. Hubertus Franke, IBM Research

Dr. Christopher J. Hughes, Intel

#### Abstract

Cloud computing is undergoing a radical transformation with the emergence of lightweight cloud-native computing paradigms, such as microservices and serverless computing. Users build their applications by combining services, benefiting from a simplified programming model and fine-grained billing. At the same time, providers consolidate many services into a smaller number of servers, improving the utilization of their infrastructure. However, the detailed characterization of cloud-native environments presented in this thesis shows that these workloads differ significantly from traditional monolithic applications. They execute services that run for short times, exhibit bursty invocation patterns, and have frequent I/O operations that cause context switches. In addition to their core logic, services also execute many auxiliary operations known as datacenter tax, such as data serialization and encryption. Finally, services have stringent tail latency bounds, requiring the slowest requests to complete within a strict deadline. These characteristics result in significant inefficiencies in performance, energy, and resource utilization when cloud-native workloads run on conventional servers with conventional software stacks, negating the paradigm's potential benefits.

The goal of this thesis is to design hardware platforms and software stacks that enable the execution of cloud-native workloads with orders of magnitude better efficiency. The first part of the thesis designs a new hardware stack for cloud-native services. It introduces  $\mu$ Manycore, a CPU architecture that minimizes the tail latency of cloud-native services. The thesis then extends the architecture with HardHarvest to boost utilization via hardware-based core harvesting, and refines the microarchitecture with Mosaic for better performance under frequent context switches. Finally, this thesis integrates on-package accelerators into the architecture and proposes AccelFlow, a framework that enables fine-grained, low-overhead orchestration of accelerators to reduce the datacenter tax in cloud-native environments.

To maximize the efficiency of the proposed hardware architecture, the second part of the thesis builds a full software stack that is tightly co-designed with the hardware. It begins with MXFaaS, a mechanism that improves resource utilization by efficiently multiplexing resources during bursts of same-function invocations. Then, it integrates the novel Concord distributed caching system for FaaS environments, and uses SpecFaaS to accelerate end-to-end application workflows through speculative service execution. Finally, this thesis improves the energy efficiency of cloud-native environments with two frameworks: EcoFaaS, which uses fine-grained scheduling and dynamic frequency scaling, and SmartOClock, which underprovisions resources and selectively overclocks cores during load spikes.

To my family, for their unconditional love and unwavering support.

## Acknowledgments

First, I would like to express my deepest gratitude to my PhD. advisor, Professor Josep Torrellas, for his invaluable guidance, support, and the many opportunities he provided throughout my PhD journey. His mentorship taught me how to conduct high-quality research while encouraging me to pursue the areas that genuinely excited me. He showed me the importance of persistence and resilience, always reminding me never to give up. I vividly remember the many times I felt lost, questioning whether a PhD in Computer Science was the right path for me. During those moments, Josep was always ready to meet, offering encouragement and perspective. Our conversations helped me lift my head above the challenges and continue growing, developing what he fondly called "elephant skin." I will always remember the countless Zoom meetings preparing camera-ready papers, the practice talks before conferences, and his exceptional support during my academic job search. His dedication to mentoring and belief in my potential have left a lasting impact.

I am also grateful to Professor Tianyin Xu for his encouragement and support throughout my PhD journey. He consistently cheered for me, believed in my abilities, and helped me achieve my goals. I remember our meetings in his office during the early years of my PhD, where he patiently taught me how to write papers—how to tell a compelling story while maintaining both technical depth and breadth. Tianyin also gave me the opportunity to mentor younger students, an experience through which I grew tremendously.

I would also like to thank Dr. Hubertus Franke for his collaboration and advice throughout my PhD. From the early stages of my research, I had the privilege of working with Hubertus on several projects, including a memorable summer at IBM Research under his guidance. His energy, enthusiasm, and readiness to take on new challenges were inspiring. Through these experiences, I learned how to effectively pitch my research and present my ideas to a wide range of audiences—from domain experts to patent lawyers.

I am also deeply thankful to Professor Dimitrios Skarlatos for his mentorship and support throughout my PhD. When I was first accepted to UIUC, Dimitris was finishing his own PhD in the same lab and played an important role in helping me get started with research. We worked together on my first project, and his guidance during those early days was invaluable. Over the years, he continued to be a trusted mentor—always ready to offer advice, share his experiences, and help me navigate the many challenges of graduate school. His feedback on my academic job market materials was incredibly helpful, and I am especially grateful for the many hours he spent patiently helping me weigh my options and make decisions.

Towards the end of my PhD, I had the opportunity to collaborate with Dr. Christopher Hughes, from whom I learned a great deal about computer architecture and how to frame research ideas in ways that are both exciting and practical within the production constraints of large companies such as Intel. Chris was always ready to review paper drafts, offer thoughtful feedback, and engage in in-depth discussions about next steps and how to strengthen our work. His intelligence, energy, and kindness made working with him an incredibly rewarding experience, and I am grateful for everything I learned through our collaboration.

Next, I would like to thank the rest of my committee members—Professor Christina Delimitrou, Professor Darko Marinov, and Professor Jian Huang—for their support and valuable feedback throughout my PhD. Professor Delimitrou's work has always been a source of inspiration for me. Her research on benchmarking and analyzing cloud workloads sparked many ideas and directions in my own work, and I have long admired her contributions to the field. Professor Marinov was one of my earliest contacts at UIUC, as we share the same home country and undergraduate institution. His cheerful spirit, energy, and willingness to help made a lasting impression on me. Professor Huang served on the committees for all of my major milestones—qualifying exam, preliminary exam, and final defense—and his insightful comments and feedback consistently helped me strengthen my research and broaden my perspectives. I am grateful for their time, mentorship, and encouragement.

I would also like to thank the Microsoft Azure Research Systems group, and in particular the colleagues I closely collaborated with: Dr. Chaojie Zhang, Dr. Esha Choukse, Dr. Iñigo Goiri, Dr. Haoran Qiu, Dr. Enrique Saurez, Dr. Pulkit Misra, Dr. Sam Whitlock, Dr. Rodrigo Fonseca, and Dr. Ricardo Bianchini. I had the opportunity to spend two summers at Azure, working on exciting projects that shaped my research interests and skills. I am grateful for all the help, advice, and mentorship I received, and I appreciate how our collaborations continued even beyond the internship periods.

I would also like to thank the current and past members of the i-acoma research lab: Apostolos, Dimitris Skarlatos, Serif, Neil, Nam, Antonis, Makis, Dingyuan, Nikoleta, Chase, Burak, Jacob, Chloe, Abe, Shashwat, Filippos, and Dimitris Merkouriadis. We shared many memorable moments—whether in the office, at group seminars, during conference trips, or simply outside of research, where I made real and lasting friendships.

Whenever I needed help with anything related to graduate school, housing, traveling, or anything else, I could always rely on Apostolos, whose kindness and willingness to help meant a great deal to me. As I mentioned earlier, Dimitris was a constant and important figure throughout my PhD journey. Neil was immensely helpful when it came to organizing my job application materials, providing feedback, and always offering support; I am excited that we will continue our careers at the same institution. Antonis and I started our Ph.D.s

together—he is a great friend and a roommate, both in Champaign and during our internships, where we shared unforgettable experiences. Makis is a close friend with whom I shared many wonderful memories, from going out in Champaign to traveling for conferences; his constructive feedback and support in my research were always greatly appreciated. Chloe joined our lab later as a postdoc; I learned a lot from her, and I will always be grateful for her warm heart, thoughtful advice, and readiness to listen and help. I also want to thank the new students of i-acoma I had the chance to collaborate with and become friends with during my later years—Dimitris, Filippos, and Abe.

I would also like to thank my friends—those from my hometown, childhood, high school, and undergraduate years: Ana, Dusan, Neda, Nemanja, Jovana, Anja, and Aleksandra. Thank you for always being there for me, for supporting me, and for welcoming me back with open arms no matter how much time had passed. Thank you for celebrating the good moments with me and helping me through the challenges. I am deeply grateful; this journey would never have been the same without you. In addition, I want to thank the new friends I made during my PhD, including the i-acoma group, Anna, and Ben, whose support and friendship made the experience even more meaningful.

A special thank you to Nikoleta for being there through it all—whether it was tackling research challenges, sharing daily ups and downs, traveling together to explore new places, or making each other's tough days feel lighter and each other's successes feel even sweeter. Having you alongside made this whole experience easier, a lot more fun, and truly memorable. I'm grateful we got to go through this together.

Finally, I want to thank my family. My parents, Dragana and Ivan, and my sister, Nevena, have always been my biggest supporters and the foundation of my journey. They have always believed in me, even from afar. No matter how difficult it was in the early years to go to the airport and travel to the other side of the ocean, I always knew that I had a home to return to and unwavering support behind me. There is absolutely no way I would be where I am today without them. Their love, sacrifices, and belief in me have made everything possible, and I am forever grateful.

This work was supported by NSF under grants CNS 1956007, CCF 2107470, and CCF 2316233; by Intel Corporation under the Transformative Server Architectures (TSA) Center; by the IBM-Illinois Discovery Accelerator Institute; and by ACE, one of the seven centers in JUMP 2.0, a Semiconductor Research Corporation (SRC) program sponsored by DARPA.

# TABLE OF CONTENTS

| CHAPT | TER 1 Thesis Overview                                                     |

|-------|---------------------------------------------------------------------------|

| 1.1   | Hardware for Cloud-Native Services                                        |

| 1.2   | Software for Cloud-Native Services                                        |

| 1.3   | Impact of this Thesis                                                     |

| CHAPT | TER 2 General Background on Cloud-Native Services                         |

| 2.1   | Microservice Environments                                                 |

| 2.2   | Serverless Platforms                                                      |

| CHAPT | TER 3 Processor Architecture for Tail Latency of Cloud-Native Services 10 |

| 3.1   | Introduction                                                              |

| 3.2   | The Need for a Cloud-Native CPU                                           |

| 3.3   | Characterizing Microservices on Current Processors                        |

| 3.4   | $\mu$ Manycore: A Cloud-Native CPU                                        |

| 3.5   | Methodology                                                               |

| 3.6   | Evaluation                                                                |

| 3.7   | Related Work                                                              |

| 3.8   | Further Enhancements                                                      |

| 3.9   | Conclusion                                                                |

| CHAPT | TER 4 Hardware Support for Core Harvesting of Cloud-Native Services 37    |

| 4.1   | Introduction                                                              |

| 4.2   | Background                                                                |

| 4.3   | Motivation for In-Hardware Core Harvesting                                |

| 4.4   | HardHarvest: Core Harvesting in Hardware                                  |

| 4.5   | Methodology                                                               |

| 4.6   | Evaluation                                                                |

| 4.7   | Related Work                                                              |

| 4.8   | Conclusion                                                                |

| CHAPT | TER 5 Microarchitecture for Cloud-Native Services                         |

| 5.1   | Introduction                                                              |

| 5.2   | Characterizing Serverless Workloads on Current Processors                 |

| 5.3   | Mosaic: Server Architecture Co-Design for Serverless Functions            |

| 5.4   | Methodology                                                               |

| 5.5   | Evaluation                                                                |

| 5.6   | Related Work                                                              |

| 5.7   | Conclusion                                                                |

| CHAP                                                                                                                 | ΓER 6 Domain-Specific Accelerators for Cloud-Native Services                                                                                                                                                                                                                                                                                                                                                                  | 96                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| 6.1                                                                                                                  | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                  | 96                                                                                                    |

| 6.2                                                                                                                  | Background                                                                                                                                                                                                                                                                                                                                                                                                                    | 97                                                                                                    |

| 6.3                                                                                                                  | Characterizing Accelerators for Microservices                                                                                                                                                                                                                                                                                                                                                                                 | 98                                                                                                    |

| 6.4                                                                                                                  | AccelFlow: Orchestrating Accelerators                                                                                                                                                                                                                                                                                                                                                                                         | 103                                                                                                   |

| 6.5                                                                                                                  | Detailed AccelFlow Implementation                                                                                                                                                                                                                                                                                                                                                                                             | 111                                                                                                   |

| 6.6                                                                                                                  | Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                    | 114                                                                                                   |

| 6.7                                                                                                                  | Related Work                                                                                                                                                                                                                                                                                                                                                                                                                  | 122                                                                                                   |

| 6.8                                                                                                                  | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                    | 122                                                                                                   |

| CHAP                                                                                                                 | ΓER 7 Efficient Resource Utilization in Cloud-Native Services                                                                                                                                                                                                                                                                                                                                                                 | 123                                                                                                   |

| 7.1                                                                                                                  | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                  | 123                                                                                                   |

| 7.2                                                                                                                  | Characterizing Resource Inefficiencies in FaaS Environments                                                                                                                                                                                                                                                                                                                                                                   | 125                                                                                                   |

| 7.3                                                                                                                  | MXFaaS Overview                                                                                                                                                                                                                                                                                                                                                                                                               | 129                                                                                                   |

| 7.4                                                                                                                  | MXFaaS Design                                                                                                                                                                                                                                                                                                                                                                                                                 | 131                                                                                                   |

| 7.5                                                                                                                  | MXFaaS Implementation                                                                                                                                                                                                                                                                                                                                                                                                         | 136                                                                                                   |

| 7.6                                                                                                                  | Methodology                                                                                                                                                                                                                                                                                                                                                                                                                   | 138                                                                                                   |

| 7.7                                                                                                                  | Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                    | 140                                                                                                   |

| 7.8                                                                                                                  | Discussion                                                                                                                                                                                                                                                                                                                                                                                                                    | 146                                                                                                   |

| 7.9                                                                                                                  | Related Work                                                                                                                                                                                                                                                                                                                                                                                                                  | 147                                                                                                   |

| 7.10                                                                                                                 | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                    | 149                                                                                                   |

|                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                       |

| СНАР                                                                                                                 | CER & Software Caches for Low I/O Overheads in Cloud Native Services                                                                                                                                                                                                                                                                                                                                                          | 150                                                                                                   |

| CHAP'                                                                                                                | 1                                                                                                                                                                                                                                                                                                                                                                                                                             | 150<br>150                                                                                            |

| 8.1                                                                                                                  | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                  | 150                                                                                                   |

| 8.1<br>8.2                                                                                                           | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                  | 150<br>152                                                                                            |

| 8.1<br>8.2<br>8.3                                                                                                    | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                  | 150<br>152<br>156                                                                                     |

| 8.1<br>8.2<br>8.3<br>8.4                                                                                             | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                  | 150<br>152<br>156<br>167                                                                              |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5                                                                                      | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                  | 150<br>152<br>156<br>167<br>169                                                                       |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6                                                                               | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                  | 150<br>152<br>156<br>167<br>169<br>170                                                                |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7                                                                        | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                  | 150<br>152<br>156<br>167<br>169<br>170<br>177                                                         |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6                                                                               | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                  | 150<br>152<br>156<br>167<br>169<br>170                                                                |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>8.8                                                                 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                  | 150<br>152<br>156<br>167<br>169<br>170<br>177<br>179<br>180                                           |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>8.8<br>8.9                                                          | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                  | 150<br>152<br>156<br>167<br>169<br>170<br>177<br>179<br>180                                           |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>8.8<br>8.9<br>CHAP7                                                 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                  | 150<br>152<br>156<br>167<br>169<br>170<br>177<br>180<br>181                                           |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>8.8<br>8.9<br>CHAP<br>9.1<br>9.2                                    | Introduction  Motivation  Concord: High-Performance Caching for FaaS  Unlocking New Capabilities with Concord  Methodology  Evaluation  Comparison to a Fault-Tolerant Protocol  Related Work  Conclusion  TER 9 Software Speculation for Further Performance Gains  Introduction  Background                                                                                                                                 | 150<br>152<br>156<br>167<br>169<br>170<br>177<br>180<br>181<br>181<br>182                             |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>8.8<br>8.9<br>CHAP<br>9.1<br>9.2<br>9.3                             | Introduction  Motivation  Concord: High-Performance Caching for FaaS  Unlocking New Capabilities with Concord  Methodology  Evaluation  Comparison to a Fault-Tolerant Protocol  Related Work  Conclusion  TER 9 Software Speculation for Further Performance Gains  Introduction  Background  FaaS Workflows Characterization                                                                                                | 150<br>152<br>156<br>167<br>169<br>170<br>177<br>179<br>180<br>181<br>181<br>182<br>184               |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>8.8<br>8.9<br>CHAP<br>9.1<br>9.2<br>9.3<br>9.4                      | Introduction  Motivation  Concord: High-Performance Caching for FaaS  Unlocking New Capabilities with Concord  Methodology  Evaluation  Comparison to a Fault-Tolerant Protocol  Related Work  Conclusion  TER 9 Software Speculation for Further Performance Gains  Introduction  Background  FaaS Workflows Characterization  SpecFaaS Overview                                                                             | 150<br>152<br>156<br>167<br>169<br>170<br>177<br>179<br>180<br>181<br>181<br>182<br>184<br>187        |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>8.8<br>8.9<br>CHAP<br>9.1<br>9.2<br>9.3<br>9.4<br>9.5               | Introduction  Motivation  Concord: High-Performance Caching for FaaS  Unlocking New Capabilities with Concord  Methodology  Evaluation  Comparison to a Fault-Tolerant Protocol  Related Work  Conclusion  TER 9 Software Speculation for Further Performance Gains  Introduction  Background  FaaS Workflows Characterization  SpecFaaS Overview  SpecFaaS Design                                                            | 150<br>152<br>156<br>167<br>169<br>177<br>179<br>180<br>181<br>182<br>184<br>187                      |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>8.8<br>8.9<br>CHAP<br>9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6        | Introduction  Motivation  Concord: High-Performance Caching for FaaS  Unlocking New Capabilities with Concord  Methodology  Evaluation  Comparison to a Fault-Tolerant Protocol  Related Work  Conclusion  FER 9 Software Speculation for Further Performance Gains  Introduction  Background  FaaS Workflows Characterization  SpecFaaS Overview  SpecFaaS Design  SpecFaaS Implementation Aspects                           | 150<br>152<br>156<br>167<br>169<br>170<br>177<br>179<br>180<br>181<br>182<br>184<br>187<br>190        |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>8.8<br>8.9<br>CHAP<br>9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7 | Introduction  Motivation  Concord: High-Performance Caching for FaaS  Unlocking New Capabilities with Concord  Methodology  Evaluation  Comparison to a Fault-Tolerant Protocol  Related Work  Conclusion  FER 9 Software Speculation for Further Performance Gains  Introduction  Background  FaaS Workflows Characterization  SpecFaaS Overview  SpecFaaS Design  SpecFaaS Implementation Aspects  Experimental Methodology | 150<br>152<br>156<br>167<br>170<br>177<br>179<br>180<br>181<br>181<br>182<br>184<br>187<br>190<br>197 |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>8.8<br>8.9<br>CHAP<br>9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6        | Introduction  Motivation  Concord: High-Performance Caching for FaaS  Unlocking New Capabilities with Concord  Methodology  Evaluation  Comparison to a Fault-Tolerant Protocol  Related Work  Conclusion  FER 9 Software Speculation for Further Performance Gains  Introduction  Background  FaaS Workflows Characterization  SpecFaaS Overview  SpecFaaS Design  SpecFaaS Implementation Aspects                           | 150<br>152<br>156<br>167<br>169<br>170<br>177<br>179<br>180<br>181<br>182<br>184<br>187<br>190        |

| CHAPTER 10 Energy Management for Cloud-Native Services       | 207 |

|--------------------------------------------------------------|-----|

| 10.1 Introduction                                            | 207 |

| 10.2 Toward Energy-Efficient Serverless Environments         | 208 |

| 10.3 Limitations of Current Art                              | 214 |

| 10.4 EcoFaaS Overview                                        | 215 |

| 10.5 EcoFaaS Design                                          | 216 |

| 10.6 Methodology                                             | 224 |

| 10.7 Evaluation Results                                      | 225 |

| 10.8 Conclusion                                              | 230 |

| CHAPTER 11 Processor Overclocking for Further Energy Savings | 232 |

| 8, 44, 44, 44, 44, 44, 44, 44, 44, 44, 4                     | 232 |

|                                                              | 235 |

| 0 1 1                                                        |     |

|                                                              | 236 |

|                                                              | 242 |

|                                                              | 249 |

| $\Gamma$                                                     | 254 |

|                                                              | 256 |

| 11.8 Conclusion                                              | 257 |

| CHAPTER 12 Future Work                                       | 258 |

| CHAPTER 13 Conclusions                                       | 260 |

| APPENDIX A Other Works                                       | 261 |

| REFERENCES                                                   | 263 |

## **CHAPTER 1: Thesis Overview**

Cloud computing is undergoing a paradigm shift, as large monolithic applications are being replaced by compositions of many lightweight, loosely-coupled *microservices* [1]. Each microservice is implemented and deployed as a separate program, and executes a portion of the application's logic, such as key-value serving [2], protocol routing [3], or ad serving [4]. This composable application design simplifies development and enables programming language and framework heterogeneity. Moreover, each microservice can be shared among multiple applications, while being scaled and updated independently. This new paradigm is being embraced by major IT companies, such as Amazon, Netflix, Alibaba, Twitter, Uber, Facebook, and Google [5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16]. In addition, there are many open-source systems that manage microservices, such as Kubernetes [17] and Docker Compose [18].

Building on the microservices model, serverless or Function-as-a-Service (FaaS) computing represents the next evolution in cloud-native design. It retains the modular, functionally decomposed structure of microservices, while significantly simplifying their deployment and management. Instead of requiring developers to provision and manage the infrastructure for each microservice, serverless platforms allow users to upload individual functions, with the cloud provider handling the runtime environment, system services, and scaling. Each function runs in an ephemeral, stateless container or micro virtual machine (VM) that is created and scheduled on demand in an event-driven manner. In this environment, applications can achieve high resource utilization, scale seamlessly, and benefit from fine-grained billing. Today, serverless cloud services are offered by all major cloud providers [19, 20, 21, 22] and are widely used in domains such as e-commerce [23, 24], image and video processing [25, 26], and machine learning inference and training [27, 28, 29], among many others [30].

However, after characterizing cloud-native environments, I observed that these workloads differ significantly from traditional monolithic applications. They execute services that run for short times, exhibit bursty invocation patterns, and have frequent I/O operations that cause context switches. Moreover, in addition to their core logic, services execute many auxiliary operations known as datacenter tax, such as data serialization and encryption. Finally, services have stringent tail latency bounds, requiring the slowest requests to complete within a strict deadline. These characteristics result in significant inefficiencies in performance, energy, and resource utilization when cloud-native workloads run on conventional servers with conventional software stacks, negating much of the paradigm's potential benefit.

Therefore, the goal of this thesis is to design hardware platforms and software stacks that enable the execution of cloud-native workloads with orders of magnitude better efficiency.

## 1.1 HARDWARE FOR CLOUD-NATIVE SERVICES

Cloud-native services demand hardware that prioritizes tail latency, fine-grained execution, and dynamic resource management. To address these needs, I designed a new architectural stack that, while remaining general-purpose, it is optimized for the unique properties of cloud-native environments. I first designed  $\mu Manycore$ , a processor architecture that minimizes the tail latency of cloud-native services. Then, I extended it with HardHarvest to boost utilization through hardware-based core harvesting, and refined the microarchitecture with Mosaic for better performance under frequent context switches. Finally, I integrated on-package accelerators into this architecture and proposed AccelFlow, a framework that enables fine-grained, low-overhead orchestration of accelerators to reduce the datacenter tax in cloud-native environments.

$\mu$ Manycore [31](Chapter 3). Microservice environments execute short service requests that interact with one another via remote procedure calls (often across machines), and are subject to stringent tail-latency constraints. In contrast, current processors are designed for traditional monolithic applications. They support global hardware cache coherence, provide large caches, incorporate microarchitecture for long-running, predictable applications (such as advanced prefetching), and are optimized to minimize average rather than tail latency.

To address this imbalance, I designed  $\mu$ Manycore, an architecture optimized for microservice environments. Based on a characterization of microservice applications,  $\mu$ Manycore is designed to specifically target overheads that hurt tail latency. First, as services are relatively small but users invoke many of them concurrently,  $\mu$ Manycore does not rely on having only a few large cores. Instead, it incorporates many small cores for the same total power and area budget. As a result, the system reduces queuing without substantially hurting single-request performance.

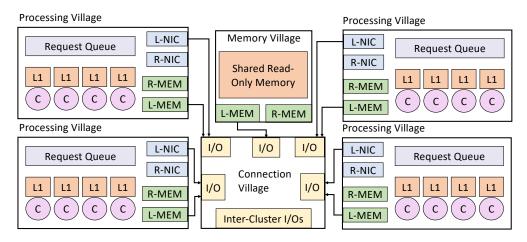

Providing many core-wide cache coherence is expensive. In fact, it is hardly needed, as microservices hardly use shared memory to communicate. Hence, rather than supporting many core-wide hardware cache coherence,  $\mu$ Many core has multiple small hardware cache-coherent domains, called *Villages*. In a village, services can communicate using shared memory, while across villages, they communicate using network messages.

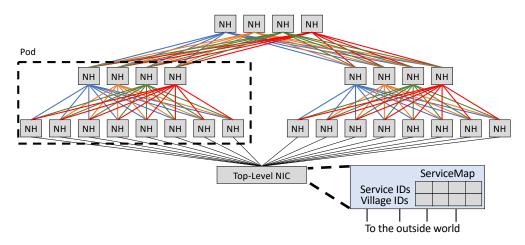

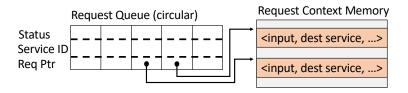

Clusters of villages are interconnected with an on-package leaf-spine network, which has many redundant, low-hop-count paths between clusters. To minimize latency overheads,  $\mu$ Manycore schedules and queues service requests in hardware, and includes hardware support to save and restore process state when doing a context-switch.

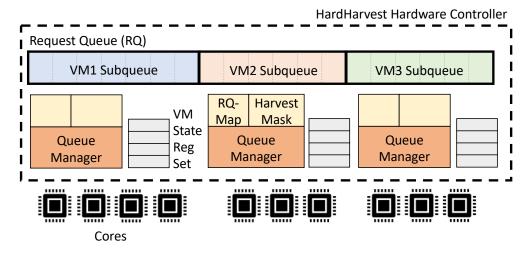

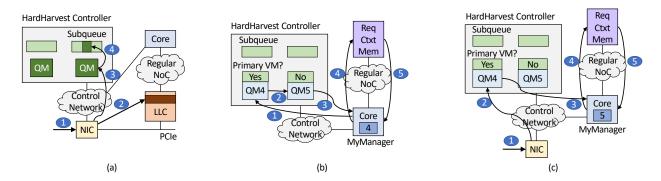

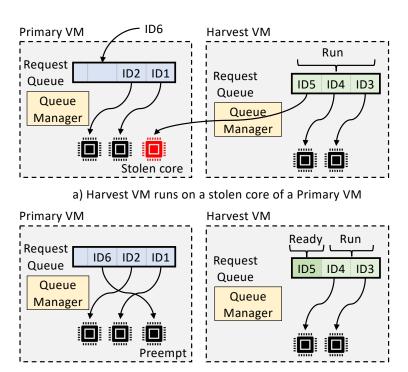

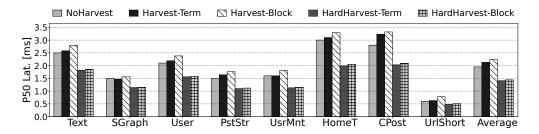

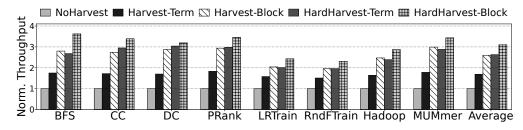

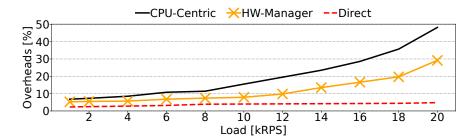

HardHarvest [32] (Chapter 4). While  $\mu$ Manycore improves tail latency for microservices, it does not tackle another critical inefficiency of these environments—chronically low core

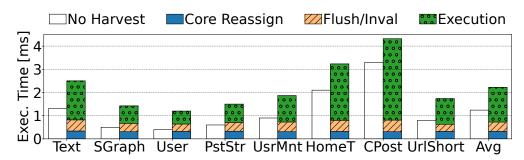

utilization due to overprovisioning for peak demand. In microservice environments, users size their virtual machines (VMs) for peak loads, leaving cores idle most of the time. To improve core utilization and overall throughput, it is instructive to consider a recently-introduced software technique for environments with relatively long running monolithic applications: Core Harvesting. With this technique, Harvest VMs running batch applications temporarily steal idle cores allocated by Primary VMs running latency-critical applications, and return them on demand. Unfortunately, re-assigning cores across VMs has substantial overhead, resulting from hypervisor calls, context switching, and flushing TLBs/caches. While such overhead is acceptable in monolithic application environments, it would be prohibitive in environments with sub-millisecond microservices.

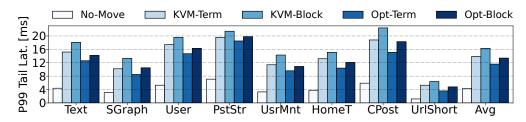

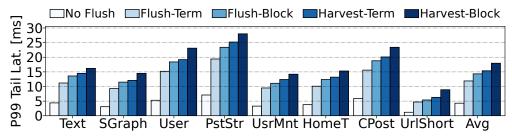

To address this problem, I designed the first architecture for core harvesting in hardware. The architecture, called HardHarvest, targets cloud-native services. It aims to: 1) maximize core utilization, 2) minimize any impact on Primary VM tail latency, and 3) boost Harvest VM throughput. Building on the  $\mu$ Manycore architecture, HardHarvest eliminates the software overheads of core harvesting by using in-hardware request scheduling, and partitioning TLBs/caches with a smart replacement algorithm.

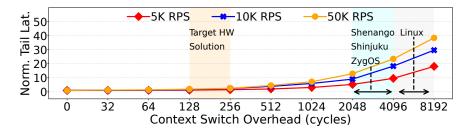

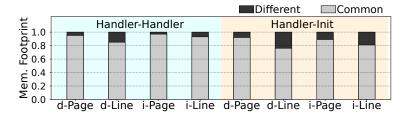

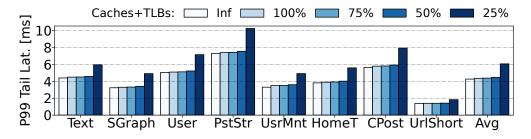

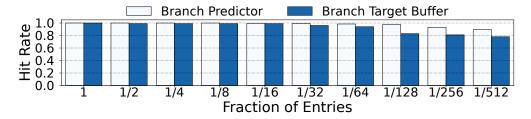

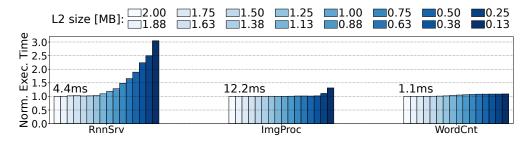

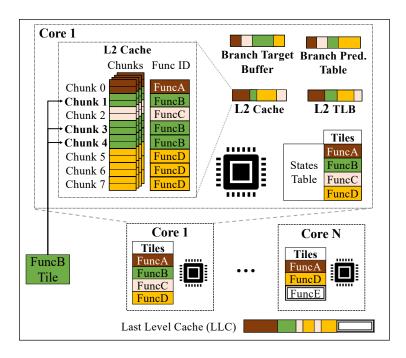

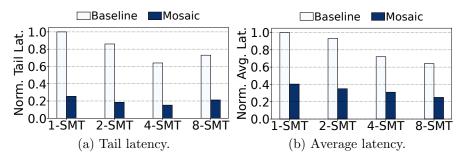

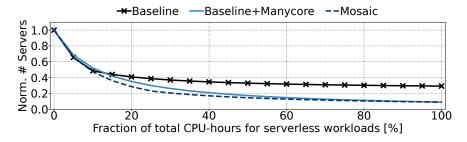

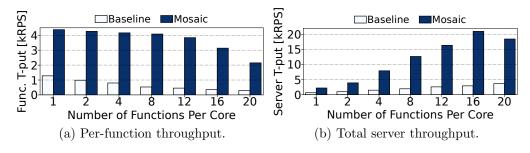

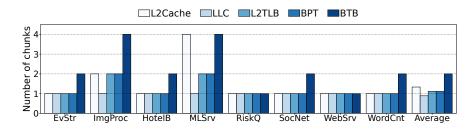

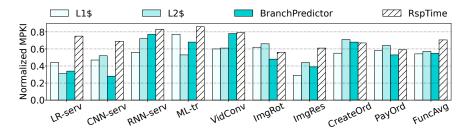

Mosaic [33](Chapter 5). As  $\mu$ Manycore provides high core counts and HardHarvest improves utilization through dynamic core sharing, the rate of context switches rises sharply, leading to persistent disruption of stateful microarchitectural structures such as caches, TLBs, and branch predictors. These structures, traditionally sized and managed for long-running applications, are poorly matched to the ephemeral and fragmented execution patterns of cloud-native services. The result is diminished performance due to lost locality, excessive misses, and increased energy usage.

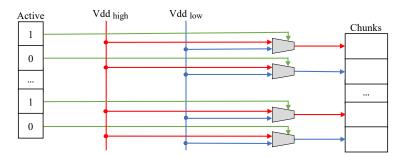

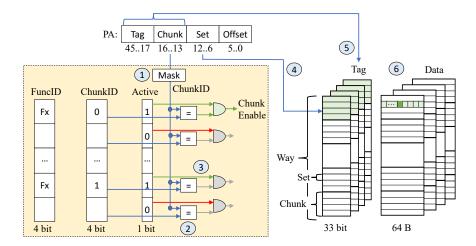

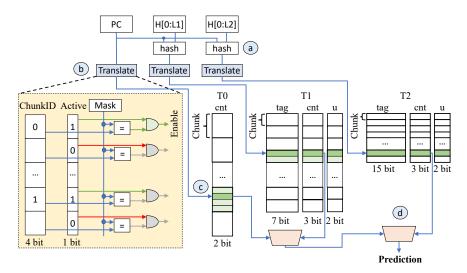

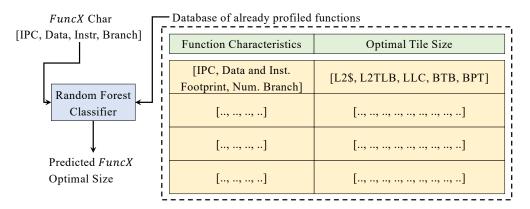

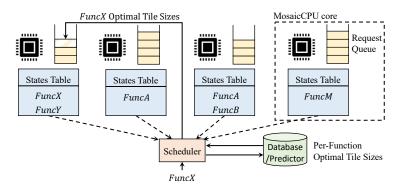

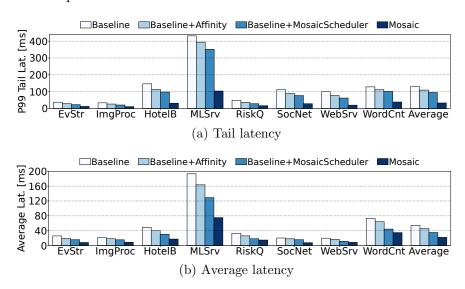

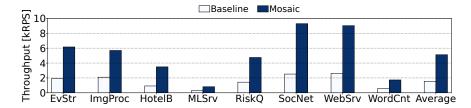

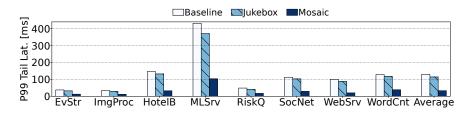

Based on these insights, I proposed *Mosaic*, a microarchitecture optimized for cloud-native environments that maintains generality to efficiently support other workloads. Mosaic has two components: (1) *MosaicCPU*, a core microarchitecture that efficiently runs both cloud-native workloads and traditional monolithic applications, and (2) *MosaicScheduler*, a software stack for cloud-native systems that maximizes the benefits of MosaicCPU. MosaicCPU slices micro-architectural structures into small chunks and assigns tiles of such chunks to individual services. The processor retains the state of services in their tiles across context switches, improving performance. Furthermore, currently-inactive tiles are set to a low power mode, reducing energy consumption. MosaicScheduler maximizes efficiency via predictive right-sizing of the per-service tiles, along with smart scheduling based on the state of the tiles.

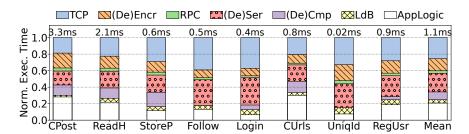

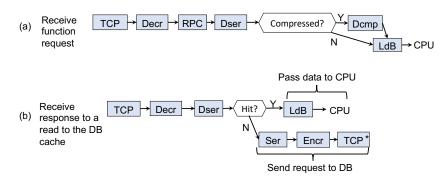

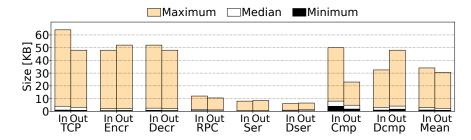

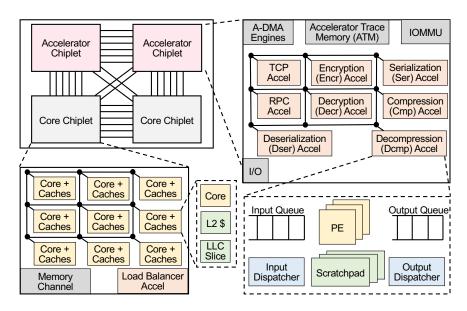

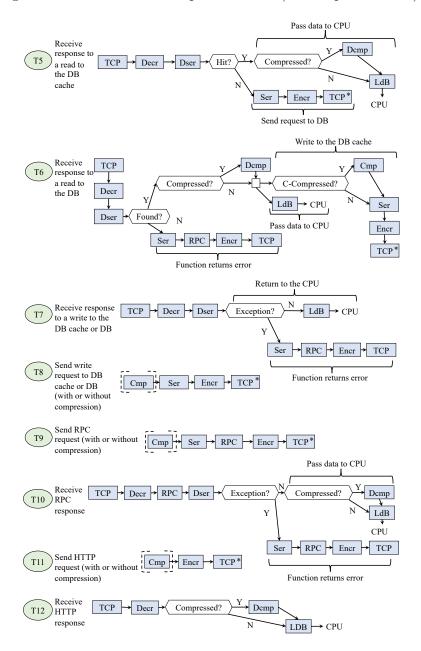

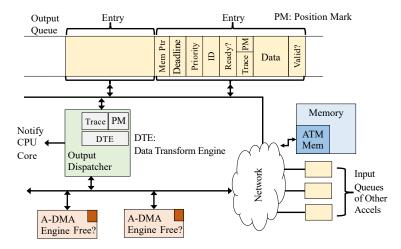

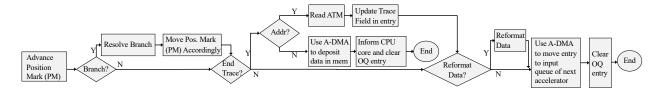

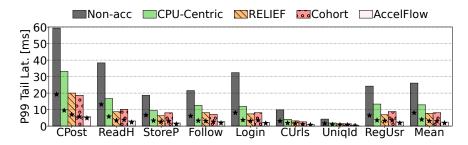

AccelFlow [34] (Chapter 6). In addition to their main application logic, cloud-native

services suffer from the execution of auxiliary operations known as datacenter tax, such as remote procedure call (RPC) processing, transmission control protocol (TCP) processing, data (de)serialization, data (de)encryption, and data (de)compression. To minimize this tax, multiple hardware accelerators have been proposed. However, it is unclear how these accelerators should be orchestrated. Past work has focused only on orchestrating accelerators in coarse-grained environments with monolithic applications.

By characterizing the needs of orchestrating an ensemble of on-package accelerators in cloud-native environments, I observed that such orchestration frameworks need to be highly dynamic and nimble. The sequences of accelerators vary across invocations of the same service, and the basic operations to be accelerated are fine grained, potentially taking only tens of  $\mu$ s. Moreover, the sequence of accelerators is often affected by "branch conditions" whose real-time resolution determines the set of subsequent accelerators needed. To address these challenges, I designed AccelFlow, the first orchestration framework for on-package accelerators in cloud-native environments. In AccelFlow, CPU cores build software structures called Traces that contain sequences of accelerators to call. A core enqueues a trace in an accelerator in user mode and, from then on, the accelerators in the trace execute in sequence without CPU involvement. A trace can include branch conditions whose outcomes determine the control flow inside the trace. Overall, the requests move from one accelerator to another with minimal overheads, allowing the CPU cores to focus on the main application logic.

#### 1.2 SOFTWARE FOR CLOUD-NATIVE SERVICES

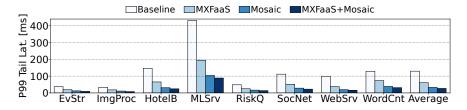

To maximize the efficiency of the proposed hardware architecture for cloud-native environments, I built a full software stack that is tightly co-designed with the hardware. I began with MXFaaS, a mechanism that improves resource utilization by efficiently multiplexing resources during bursts of same-function invocations. I also integrated a distributed caching layer called Concord to reduce overheads from frequent remote storage accesses. I then accelerated end-to-end application workflows using speculative function execution with SpecFaaS. Finally, I improved energy efficiency with EcoFaaS through fine-grained scheduling and dynamic frequency scaling, and with SmartOClock through under-provisioning of resources and selectively overclocking cores during load spikes.

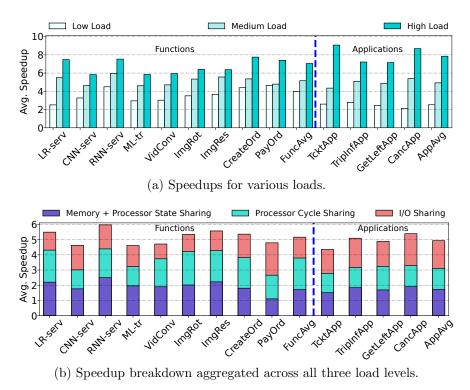

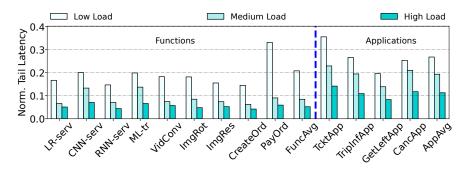

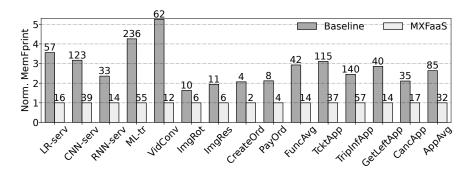

MXFaaS [35](Chapter 7). Cloud-native workloads frequently exhibit bursts of invocations of the same service. For example, different end-users can create bursts of invocations of popular services, triggered by certain events. Alternatively, a single end-user may issue thousands of invocations of the same service to parallelize data processing. Such pattern is

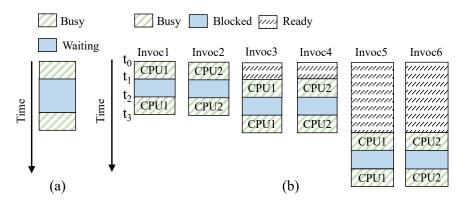

not handled well by current serverless platforms, which end up spawning many containers. Supporting this invocation pattern efficiently can speed-up serverless execution substantially and improve the resource utilization of serverless environments.

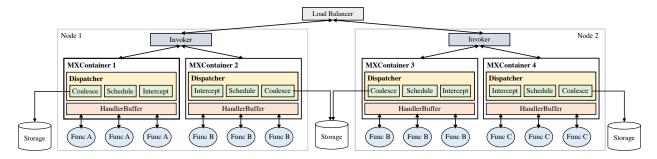

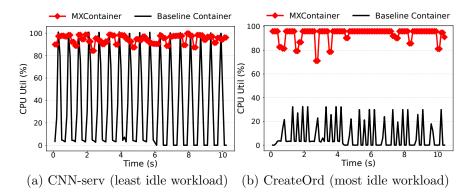

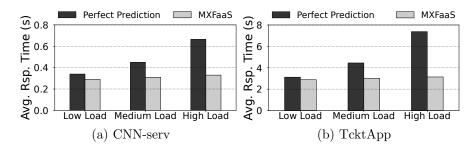

I target this dominant pattern with a new serverless platform design named MXFaaS. MXFaaS improves function performance by efficiently multiplexing (i.e., sharing) processor cycles, I/O bandwidth, and memory/processor state between concurrently executing invocations of the same function. MXFaaS introduces a new container abstraction called MXContainer. To enable efficient use of processor cycles, an MXContainer carefully helps schedule same-function invocations for minimal response time. To enable efficient use of I/O bandwidth, an MXContainer coalesces remote storage accesses and remote function calls from same-function invocations. Finally, to enable efficient use of memory/processor state, an MXContainer first initializes the state of its container and only later, on demand, spawns a process per function invocation, so that all invocations can share unmodified memory state and hence minimize memory footprint.

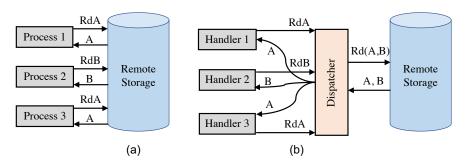

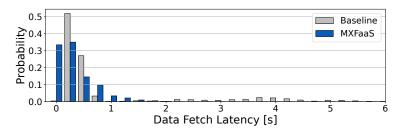

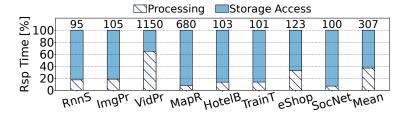

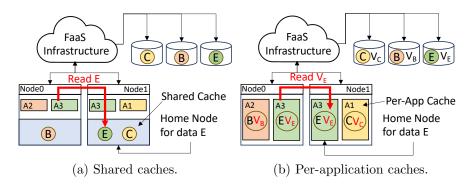

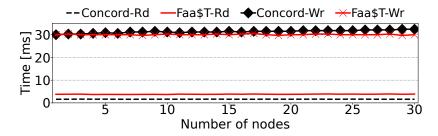

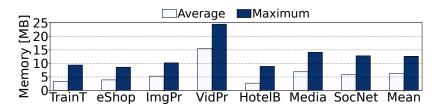

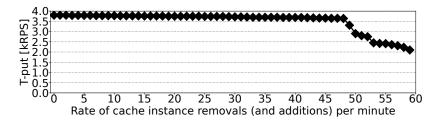

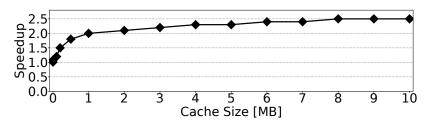

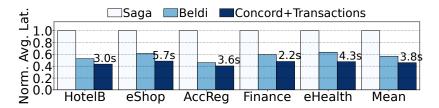

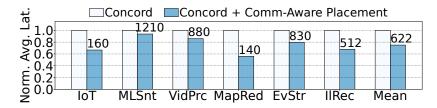

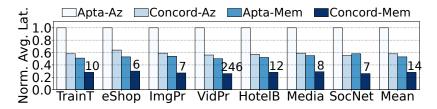

Concord [36] (Chapter 8). With MXFaaS, functions reduce their startup times and improve resource utilization through efficient multiplexing, but their individual performance remains bound by frequent accesses to remote global storage. Costly accesses to global storage substantially limit the performance of serverless functions. To mitigate this overhead, data can be cached in the memory of the nodes where functions are executed. However, existing caching schemes either (1) restrict a data item to be cached in a single node, causing frequent remote reads or (2) allow a data item to be cached in multiple nodes concurrently, adding substantial overhead to maintain cache coherence. These current approaches are suboptimal for the access patterns present in serverless workloads, which are characterized by frequent reads to small data items, strong temporal locality, and a small number of nodes concurrently executing functions of the same application.

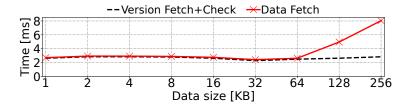

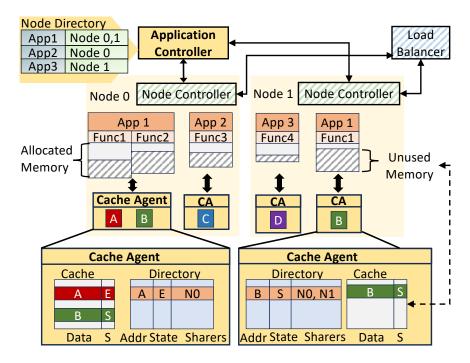

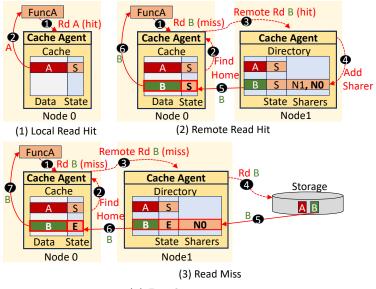

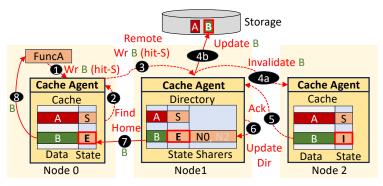

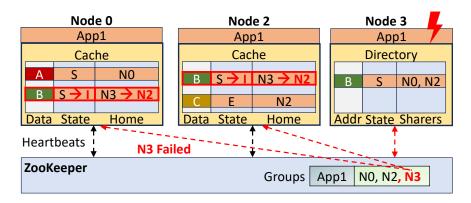

Driven by these insights, I proposed *Concord*, a distributed software caching system tailored to serverless environments. Concord uses MXFaaS within a node, and scales to a distributed setup. It allows multiple copies of the same data item to be cached in different nodes concurrently, allowing each cache to satisfy local reads. To maintain coherence across software caches, Concord proposes a directory-based distributed coherence protocol. The protocol is inspired by hardware cache coherence, and is enhanced to minimize coherence traffic, reduce contention points, and be robust to node failures and frequent coherence domain changes. Further, Concord unlocked two new capabilities in serverless environments: transactional storage accesses and transparent data-aware function placement.

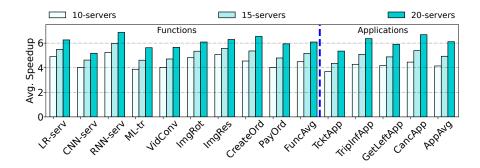

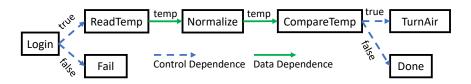

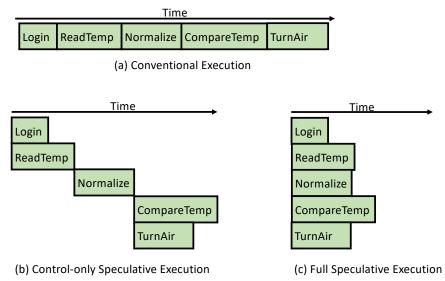

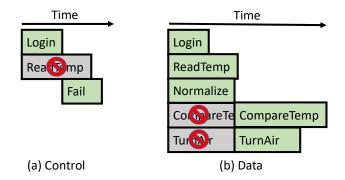

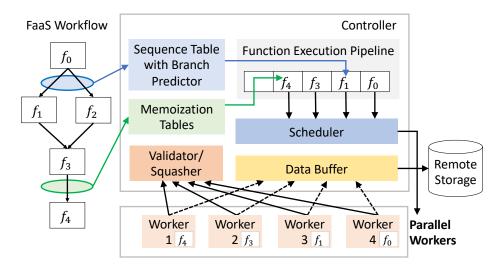

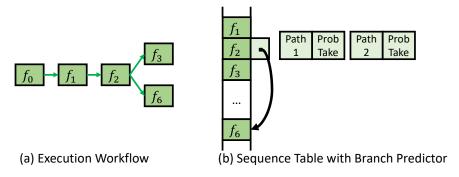

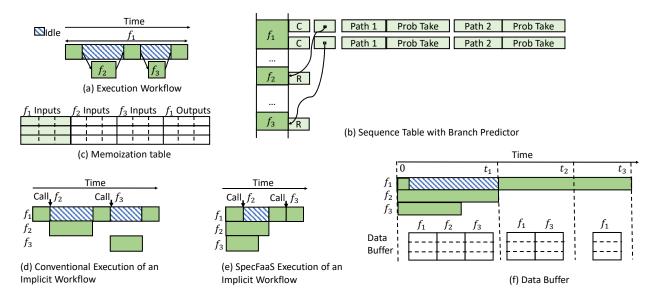

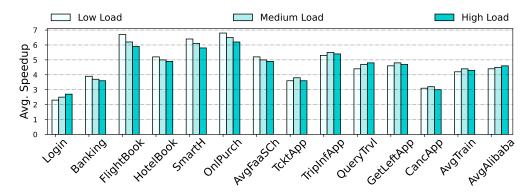

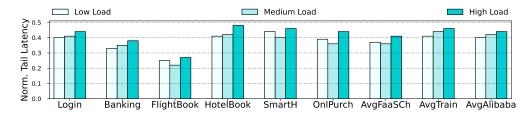

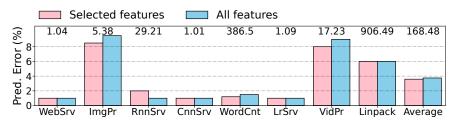

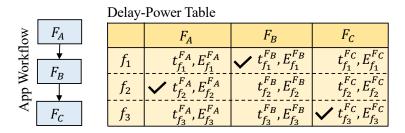

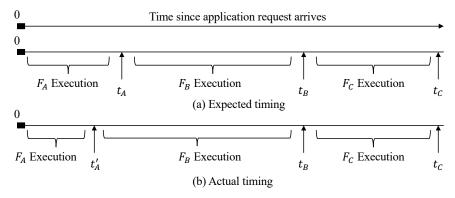

SpecFaaS [37] (Chapter 9). While improving the performance of a single function is

important, serverless applications are typically composed of multiple functions chained together. To accelerate serverless application workflows, I extended MXFaaS and Concord systems with a novel execution model based on software-supported speculative execution of functions. The proposal is termed Speculative Function-as-a-Service (SpecFaaS). It is inspired by out-of-order execution in modern processors, and is grounded in a characterization analysis of FaaS applications. In SpecFaaS, functions in an application are executed early, speculatively, before their control and data dependences are resolved. Control dependences are predicted like in pipeline branch prediction, and data dependences are speculatively satisfied with memoization. With this support, the execution of downstream functions is overlapped with that of upstream functions, substantially reducing the end-to-end execution time of applications.

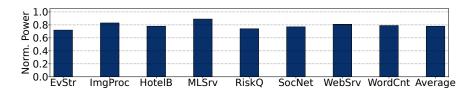

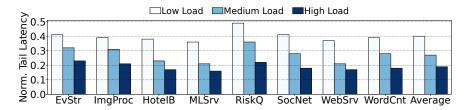

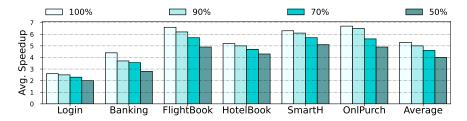

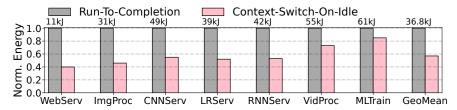

EcoFaaS [38] (Chapter 10). Serverless platforms should maintain high performance and good resource utilization while using minimal energy. Unfortunately, the energy and power consumption behavior of serverless systems has hardly been explored. Hence, I performed a thorough characterization and observed that serverless environments pose a set of challenges not effectively handled by the existing energy-management schemes. Short serverless functions execute in opaque virtualized sandboxes, are idle for a large fraction of their invocation time, context switch frequently, and are co-located in a highly dynamic manner with many other functions of diverse properties. These features are a radical shift from more traditional application environments and require a new approach to manage energy and power.

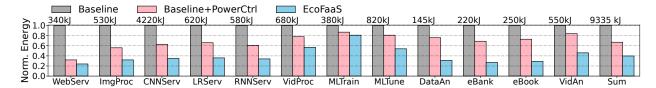

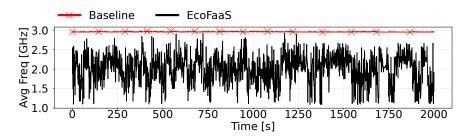

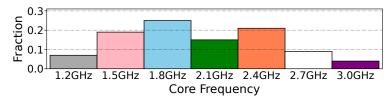

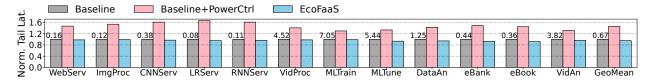

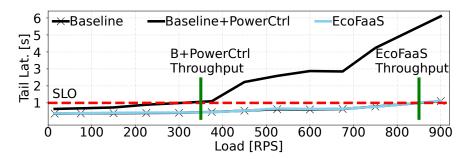

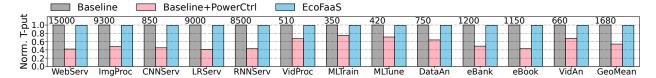

Using these insights, I extended my MXFaaS serverless platform design with *EcoFaaS*, the first energy management framework for serverless environments. EcoFaaS takes a user-provided end-to-end application Service Level Objective (SLO). It then splits the SLO into per-function deadlines that minimize the total energy consumption. Based on the computed deadlines, EcoFaaS sets the optimal per-invocation core frequency using a prediction algorithm. The algorithm performs a fine-grained analysis of the execution time of each invocation, while taking into account the specific invocation inputs. To maximize efficiency, EcoFaaS splits the cores in a server into multiple Core Pools, where all the cores in a pool run at the same frequency and are controlled by a single scheduler. EcoFaaS dynamically changes the sizes and frequencies of the pools based on the current system state.

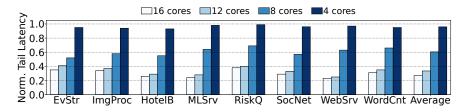

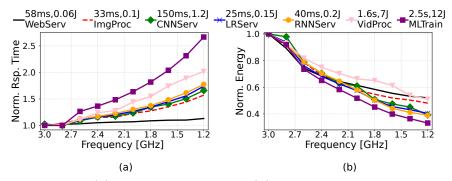

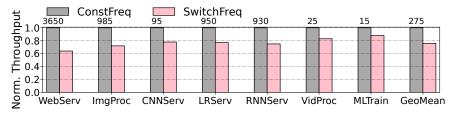

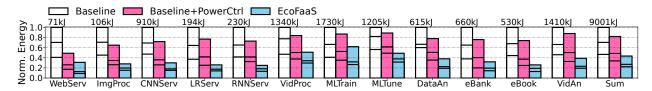

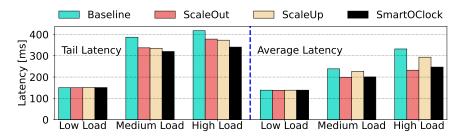

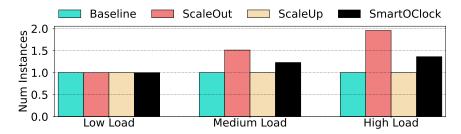

SmartOClock [39] (Chapter 11). I further enhanced the efficiency of EcoFaaS with processor overclocking during load spikes of cloud-native services. Operating server components beyond their voltage and power design limit (i.e., overclocking them) enables improved performance and lower cost for cloud-native workloads. However, overclocking can significantly degrade component lifetime, increase power draw, and cause power capping events, eventu-

ally diminishing the performance benefits.

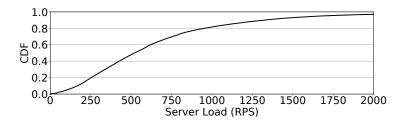

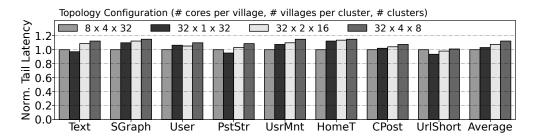

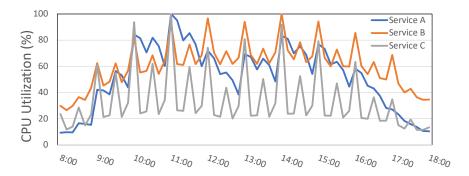

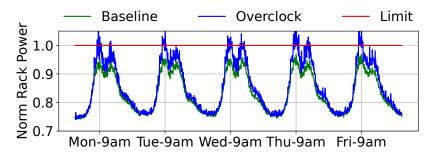

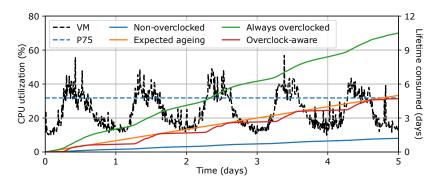

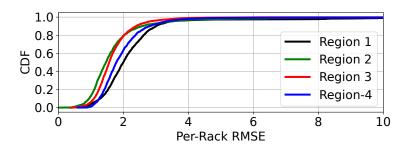

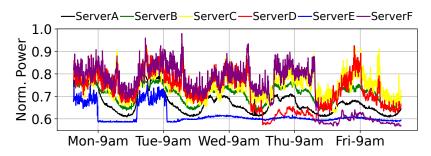

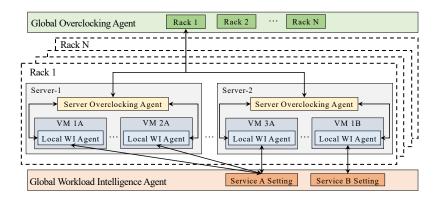

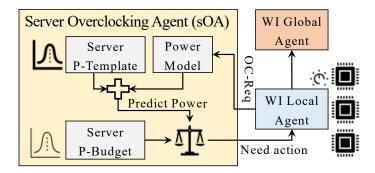

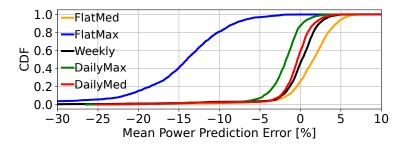

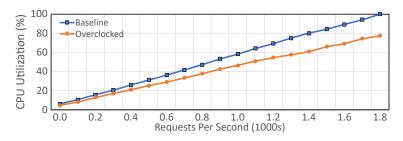

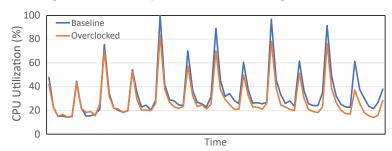

I characterized the impact of overclocking on cloud workloads by studying their profiles from Microsoft Azure production deployments. Based on the characterization, I proposed SmartOClock, the first distributed overclocking management platform specifically designed for cloud environments. The idea is to allocate the resources to cloud-native services based on their average load, and then, during load spikes, overclock the cores to compensate for resource under-provisioning. SmartOClock is a workload-aware scheme that relies on power predictions to heterogeneously distribute the power budgets across its servers based on their needs and then enforces budget compliance locally, per-server, in a decentralized manner.

## 1.3 IMPACT OF THIS THESIS

My research has helped advance cloud computing. My  $\mu Manycore$  processor architecture for microservices was recognized with an IEEE Top Picks Honorable Mention and received great attention from academia and industry partners such as Intel, IBM, and Microsoft. Further, four patents have been filed with IBM and Microsoft for my work on serverless software stack design (MXFaaS, SpecFaaS, and Concord) and processor overclocking in the cloud (SmartOClock). Building on insights from my research on cloud-native workloads, I also designed the first power and energy management systems for LLM inference in the cloud—DynamoLLM and TAPAS. Both works led to patents filed with Microsoft. Additionally, DynamoLLM was recognized with the Best Paper Award at HPCA. Notably, versions of my SmartOClock and TAPAS systems are now being implemented in Microsoft Azure production environments.

## CHAPTER 2: General Background on Cloud-Native Services

## 2.1 MICROSERVICE ENVIRONMENTS

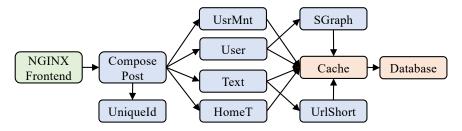

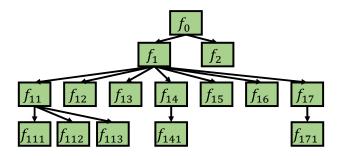

In microservice environments (e.g., managed by Kubernetes [17] or Docker Compose [18]), large complex applications are organized as workflows of multiple interdependent services. Figure 2.1 shows an example of a microservice-based application (*ComposePost*) from the DeathStarBench suite [40]. Each service, e.g., *Text* or *SGraph*, performs its dedicated functionality, communicates with other services, and scales independently of other services.

Figure 2.1: ComposePost microservice-based application. Blue boxes represent microservices. Green and orange boxes represent frontend and backend helper applications.

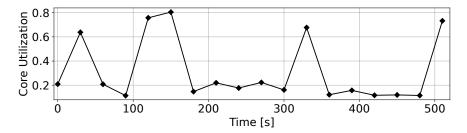

Requests for a given microservice are served by one or more *Instances* present as separate VMs or containers. When created, a VM is assigned a certain number of cores and amount of memory that it can use. Cloud providers use these resource limits to pack the VMs on servers. To accommodate the peak load, users typically overprovision VMs, leaving resources such as cores underutilized throughout the majority of the VM lifetime. Even when there is substantial load for the microservice, requests do not fully utilize cores, as cores often stall on synchronous RPCs to read/write to/from remote storage, or to invoke other microservices.

Often, a service request invokes one or more other services that perform simple operations and then aggregates the obtained data. Studies by Alibaba [5] and Facebook [14] show that such a multi-tier paradigm is popular in production-level microservice architectures. Services communicate with each other via RPC/HTTP protocols, such as gRPC [41] and eRPC [42]. When a service request calls another service synchronously, it waits on the results before continuing the execution. This operation also introduces potentially significant stall times.

Individual microservices are significantly simpler than their monolithic counterparts. They have a smaller memory footprint and working set, less pressure on instruction fetching, and orders of magnitude shorter execution time. However, in reality, these environments have substantial performance challenges. Short execution times and frequent, costly remote storage accesses and communication between services induce overheads that cannot be overlooked [2, 43, 44, 45, 46, 47, 48, 49, 50, 51, 52].

### 2.2 SERVERLESS PLATFORMS

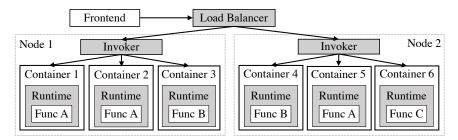

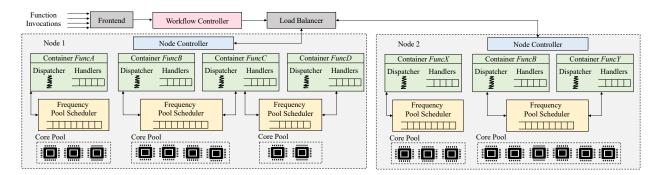

With serverless computing, developers still follow the microservice-based software architecture. Additionally, developers focus only on the main application logic, while cloud providers are in charge of provisioning all the resources and infrastructure needed to run such serverless applications. Figure 2.2 illustrates a typical architecture of a serverless platform, such as OpenWhisk, KNative, OpenFaaS, or OpenLambda [53, 54, 55, 56, 57, 58, 59, 60]. A platform consists of centralized control modules (e.g., the *frontend* and the *load balancer*) that accept function invocations and distribute them to the nodes. In each node, there is an *invoker* module that is responsible for the execution of the function.

Figure 2.2: Overview of conventional serverless platforms.

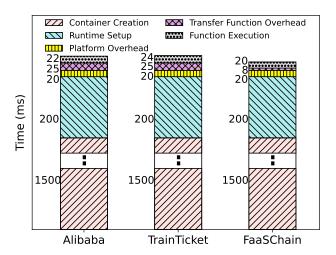

To execute a user-provided function, an invoker encapsulates the function code together with an execution runtime in a container, and spawns the runtime process [61]. The user function is executed inside the address space of the runtime process [62]. The runtime process first executes initialization code to set up network connections and initialize global variables. Then, it invokes the requested function. The runtime only services one request (i.e., one function invocation) at a time. To execute multiple invocations of the same function concurrently, production-level platforms need to spawn multiple containers.

When a function invocation completes, the serverless platform keeps the container in memory in warm state for a certain period of time [63, 64, 65]. If, during this period, another request for the same function is received, it is executed by the runtime process in the warm container. However, with this approach, the global state of the runtime process is sequentially shared across function invocations. Such sharing may lead to security and correctness issues [62].

## CHAPTER 3: Processor Architecture for Tail Latency of Cloud-Native Services

#### 3.1 INTRODUCTION

Microservice environments have new characteristics that impact the system and hardware architecture of the platforms on which they run. Specifically, requests for microservices in an application are typically short-running and may execute on different machines. Requests for different microservices share no memory state and interact with one another via remote procedure calls (RPCs) [41, 42]. Further, requests have small working sets and are often invoked in bursts, frequently waiting in queues before being executed. Finally, the decomposition of an application places tight sub-ms latency Service Level Objectives (SLOs) on individual services [2, 50]. As a result, while reducing average latency and improving throughput are important, the key performance target in these environments is now minimizing tail latency [66] (e.g., improving the 99th-percentile responses). Many of these characteristics are also found in emerging deployment methods based on microservices, such as Function-as-a-Service (FaaS) environments [19, 20, 21, 22].

Current processors are not expressly designed for these environments. Indeed, multicores invest significant hardware and design complexity to support global hardware cache coherence. They have large caches to capture the working sets of long-running applications. They are relatively unconcerned with supporting short-running, RPC-communicating programs. Instead, they incorporate microarchitectural optimizations for long-running, predictable applications, such as advanced prefetchers and branch predictors. These optimizations add significant hardware complexity and are, at best, marginally effective for microservices. Perhaps most importantly, current processors are highly optimized to minimize the average latency of programs or transactions, and ignore tail-latency considerations.

How should one change the design of processors so that they match microservice requirements? First, some of the hardware optimizations that introduce design complexity and are hardly needed by microservices, such as global hardware cache coherence, should be reconsidered. Second, there should be a comprehensive effort to optimize for tail-latency reduction. Optimizations should target both inefficiencies affecting all requests, and contention-based overheads that may affect a subset of requests. The resulting processor might not be competitive for general-purpose loads, it can be the CPU of choice for microservice datacenters.

In this chapter, we propose a processor architecture highly optimized for cloud-native microservices. We call it  $\mu Manycore$ .  $\mu Manycore$  is not an accelerator; it retains general-purpose processor capabilities, while it may not be as competitive for monolithic applications.

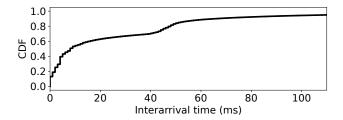

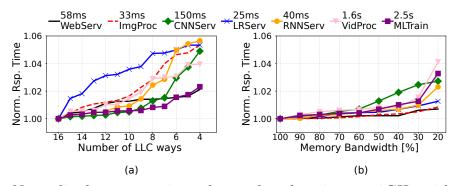

To design  $\mu Manycore$ , we first characterize production-level microservice traces from Alibaba [5] and microservices from DeathStarBench [40]. Our analysis shows that bursty service requests create periods of high demand where long waiting queues are likely to appear. In addition, requests spend most of their time blocked, waiting for the completion of their accesses to storage or their calls to other services. In the meantime, CPUs context switch frequently, introducing overhead. Moreover, service-initiated messages between cores experience the latency of interconnection networks (ICNs), often suffering contention delays that further increase tail latency. Finally, while requests have small working sets, microservices benefit from a large nearby pool of memory that stores per-service read-mostly state.

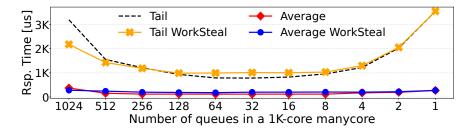

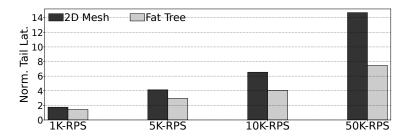

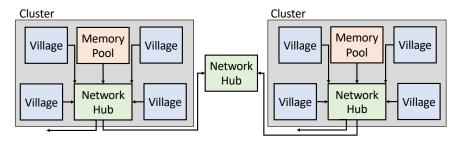

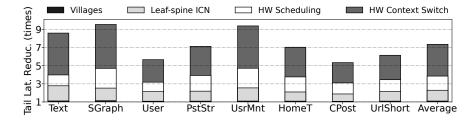

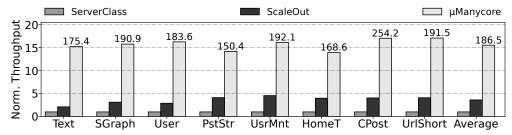

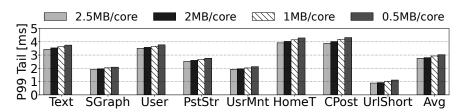

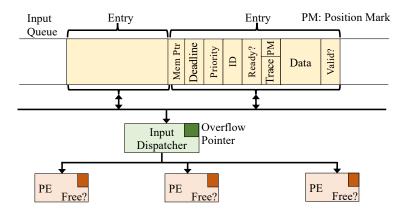

Based on these findings, we design a chiplet-based  $\mu Manycore$ . Rather than supporting package-wide hardware cache-coherence,  $\mu Manycore$  is built with multiple small hardware cache-coherent domains called *Villages*. Microservices are assigned to individual villages. A few villages, together with a memory chiplet (storing read-mostly state), are grouped in a cluster. Clusters are interconnected with a leaf-spine ICN [67, 68]. This topology has many redundant, low-hop-count paths between any two clusters—hence, minimizing contention between multiple messages with the same source and destination clusters and reducing tail latency. To minimize scheduling overheads,  $\mu Manycore$  enqueues, dequeues, and schedules service requests in hardware. Finally, to minimize the overhead of frequent context switching, cores include hardware support to save and restore process state.

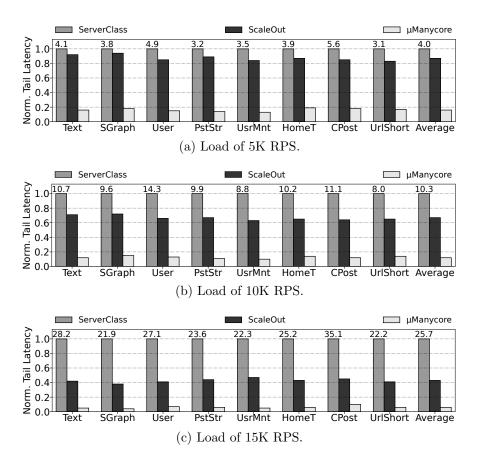

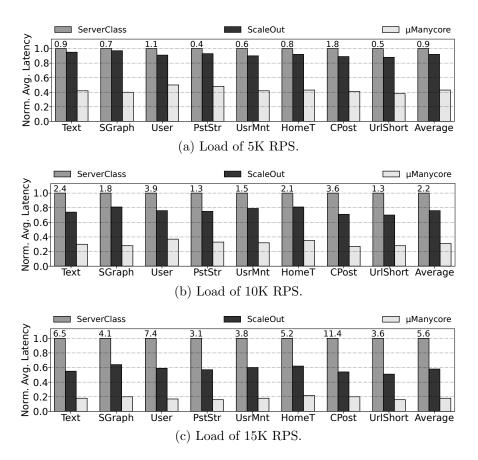

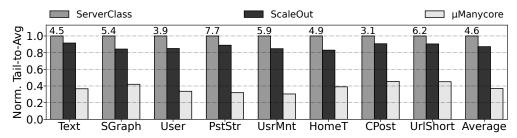

Our simulation results show that  $\mu Manycore$  delivers high performance for microservices. We compare a 1024-core  $\mu Manycore$  to two conventional server-class multicores: one with the same power and one with the same area as  $\mu Manycore$ . A cluster of 10  $\mu Manycore$  servers delivers 3.7× lower average latency, 15.5× higher throughput, and, importantly, 10.4× lower tail latency than a cluster with the iso-power conventional multicores. Similar results are attained compared to a cluster with the power-hungry iso-area conventional multicores.

This chapter makes the following contributions:

- A characterization of microservice workload behavior in conventional processors.

- µManycore, a processor architecture highly optimized for microservice workloads.

- An evaluation of  $\mu$ *Manycore*, comparing it to two conventional server-class multicores: one with the same power and one with the same area.

#### 3.2 THE NEED FOR A CLOUD-NATIVE CPU

The ever-increasing complexity of software systems has kept pushing forward processor design. For example, researchers have proposed numerous prefetching, branch prediction,

and cache replacement schemes. These proposals introduce custom microarchitectural structures that increase processor area, power consumption, and design complexity in order to improve application performance.

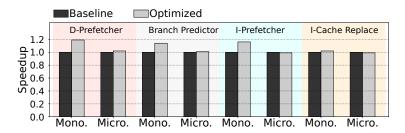

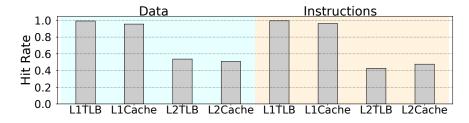

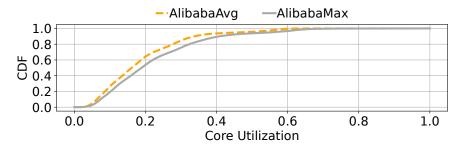

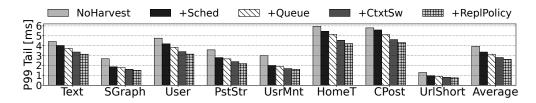

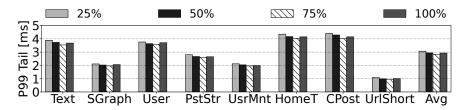

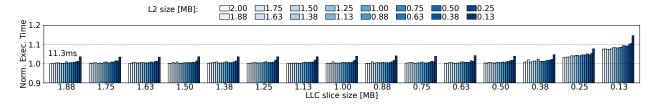

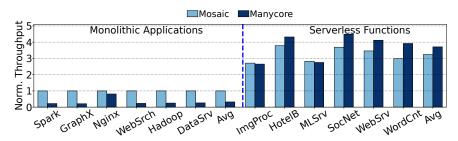

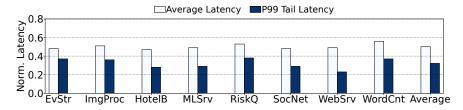

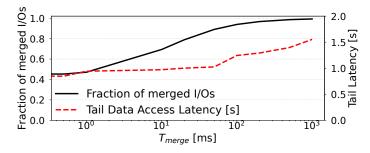

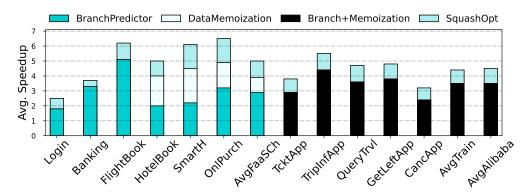

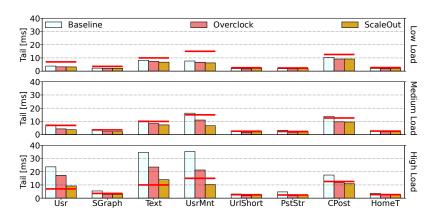

However, many of these optimizations hardly benefit cloud-native microservices. To validate this hypothesis, we consider four published microarchitectural optimizations for which the simulator and applications used in the publications are open sourced. For each of the optimizations, we first run the original applications [69, 70, 71, 72, 73] on the original simulator and record the performance with and without the optimizations. The results are depicted as bars Baseline and Optimized in Mono (for Monolithic) in Figure 3.1, normalized to Baseline. We then run a set of microservice applications—SocialNetwork from DeathStarBench [40], and Router and SetAlgebra from  $\mu$ Suite [50]—on the original simulator and record the performance with and without the optimizations. The results are depicted as bars Baseline and Optimized in Micro (for Microservice) in Figure 3.1, normalized to Baseline.

Figure 3.1: Performance improvements of four recently-proposed microarchitectural optimizations using monolithic (Mono) and microservice (Micro) applications. For each optimization and application set, the bars are normalized to Baseline.

The optimizations are as follows:

**D-Prefetcher** shows the impact of the Pythia reinforcement-learning data prefetcher [74]. Pythia speeds-up monolithic applications by 19% on average over a system without a prefetcher. However, it brings only marginal benefits of 2% to microservices.

**Branch Predictor** shows the impact of a perceptron-based branch predictor [75]. The predictor speeds-up monolithic applications by 14% on average over a system with a simple g-share predictor. On the other hand, the predictor speeds-up microservice applications by only 1% on average over the g-share predictor.

**I-Prefetcher** shows the impact of the I-SPY context-driven instruction prefetcher [76]. The prefetcher speeds-up monolithic applications by 16% on average over a system without instruction prefetcher. On the other hand, it does not speed-up microservice applications.

**I-Cache Replace** shows the impact of the Ripple profile-guided instruction cache replacement algorithm [77]. The algorithm speeds-up monolithic applications by 2% on average over

a system with LRU replacement. However, it does not bring any benefits to microservices.

The reason for the discrepancy in the effectiveness of the proposed optimizations is the reduced data and instruction memory footprint of the microservice workloads compared to the monoliths, as well as their increased cache hit rates and different branch behavior. This data shows that a different type of processor microarchitecture is needed to speed-up microservice applications.

## 3.3 CHARACTERIZING MICROSERVICES ON CURRENT PROCESSORS

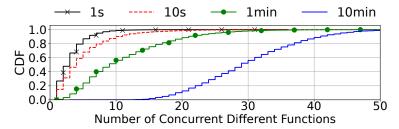

To guide the design of  $\mu Manycore$ , we first characterize the behavior of microservice applications on current processors. We execute the DeathStarBench [40], TrainTicket [78], and  $\mu$ Suite [50] open-source microservice application suites, as well as real-world production-level microservice execution traces from Alibaba [5]. Our main conclusions are described next.

## 3.3.1 Monolithic Cache Coherence Provides Limited Advantage

To enable high availability, fast scalability, and fault tolerance, microservice applications are implemented as sets of services. Each service is built as a standalone RPC/HTTP server—in our workloads, a TThreadedServer [79], RestController [80], HTTPServer [81], or gRPCServer [41]. Upon service instance initialization, network connections are set up, libraries are loaded, and preparation code is executed. Upon service request arrival, the service instance spawns a new worker (a process, thread, or co-routine) or reuses an existing one to serve the request.

Different services or different instances of the same service do not share any modifiable memory. A worker can update its private state, the local state of its service instance and, with RPC calls, the state in global storage. This is in contrast to traditional multi-threaded applications, where concurrently-running threads are often free to share memory.

Given this environment, conventional monolithic hardware cache coherence, as it is used in current large multicores, is hard to justify. Cache coherence is only needed inside a service instance, which typically uses only a few cores. One could argue that global coherence would still be needed if we allowed service instances to migrate across any cores. However, unimpeded migration of service instances across a large 1K-core multicore is unlikely to deliver performance improvements and, in fact, is likely to increase tail latency. Hence, given the well-known hardware complexity and scalability challenges of large-scale hardware cache-coherence, it is more reasonable to support only small-scale cache-coherence domains

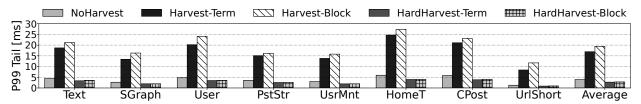

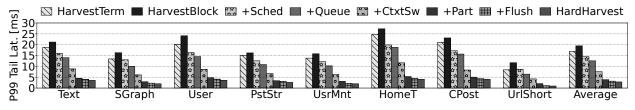

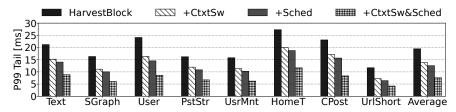

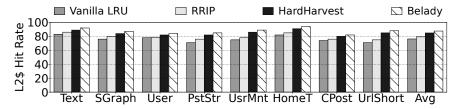

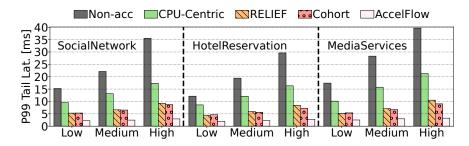

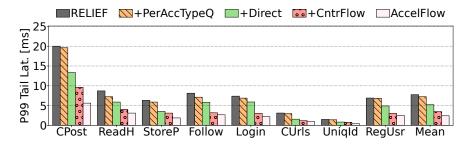

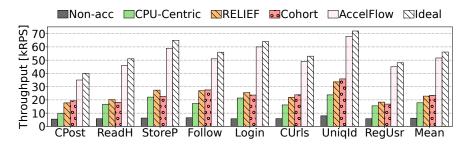

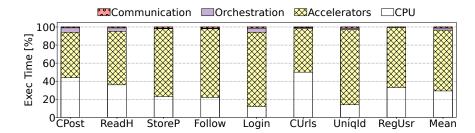

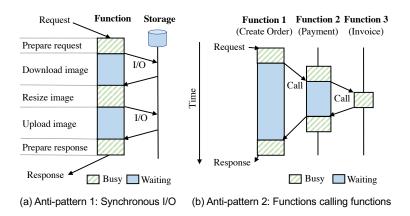

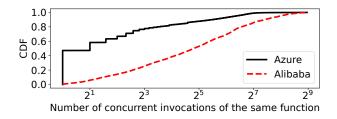

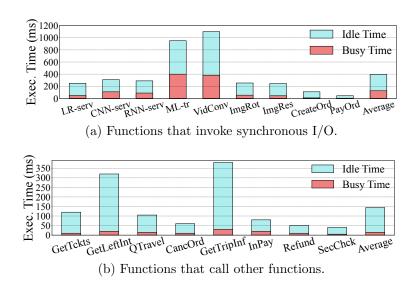

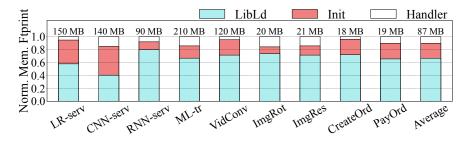

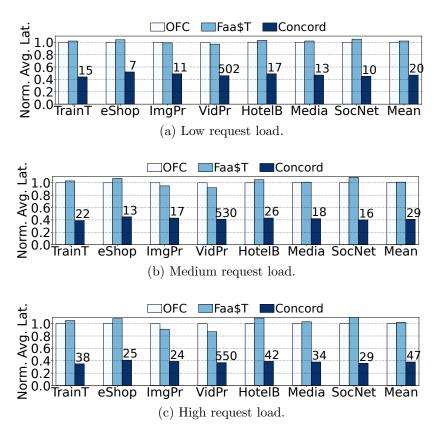

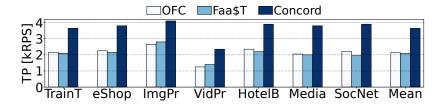

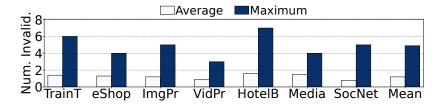

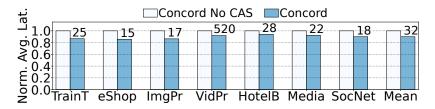

among the cores used by individual service instances. Service requests for a given instance can still migrate between the cores used by the service instance if needed for load balance—resulting in a more efficient environment.